Tema:

A Reed-Solomon Product-Code (RS-PC)

Decoder for DVD Applications

H-C. Chang, C. Shung

Introducción

Esta investigación es sobre aplicaciones del código de Reed-Salomon.

En el siguiente resumen, se muestra como se aplica el código en aplicaciones sobre formatos de DVDs.

Investigación

El DVD, era un estándar emergente, con gran capacidad para guardar audio, Reed-Salomon code se usa en los DVD para la corrección de errores.

Como se ilustra en la Figura 1, cada fotograma del código de producto que contiene 192 x l72 Bits, los datos de usuario se codifican en 208 x l82 Bits.

El chip decodificador del RS-PC se ilustra en la Figura 2. El chip decodificador contiene dos controladores de amortiguamiento, seguidos del decodificador.

En cualquier momento, el buffer primario está sirviendo los datos de entrada, los datos de salida, y el otro buffer secundario está sirviendo al decodificador RS.

Las ubicaciones y valores de errores calculados por los decodificadores RS se envían a los controladores del frame-buffer para actualizar el contenido de memoria de vídeo en consecuencia.

Esta arquitectura paralela minimiza la cantidad de acceso de memoria de vídeo y las restricciones de distribución en los decodificadores de RS.

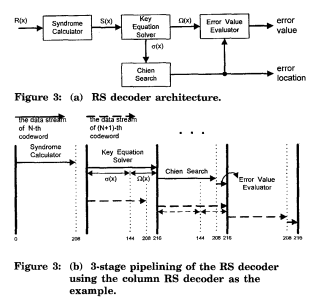

En la Figura 3 (a), se muestra cada decodificador RS que contiene una calculadora, un solucionador de claves de la ecuación, una búsqueda de Chien y un valor de evaluador de error.

La Figura 3 (b), muestra una canalización de 3 etapas, que utiliza en los decodificadores RS, donde la búsqueda de Chien y el valor evaluador de error se llevaron a cabo tanto en la tercera etapa.

El algoritmo de Berlekamp-Massey se utiliza en el solucionador de claves de ecuación, funciona con coeficientes del polinomio individuales en lugar de todo el polinomio.

Aunque más ciclos se utilizan en el algoritmo de descomposición, los tamaños del código de RS-PC son lo suficientemente grandes como para no tener pérdida de velocidad.

La figura 4 muestra la arquitectura de la ecuación-solver. Esta arquitectura de solución de ecuaciones puede ser re-configurado para calcular Q(x).

En la Figura 4, las líneas corresponden a símbolos de datos en base doble mientras que las líneas sólidas corresponden a símbolos de datos en base estándar, y D2S es un convertidor estandar.

En la figura 5 se muestra el diseño de un paralelo de entrada-salida de FFMIS. Los bloques interiores muestran el producto a implementar de Reed-Muller.

El valor evaluador de error contiene varias misiones exploratorias, una variable de FFM y uno de FFI.

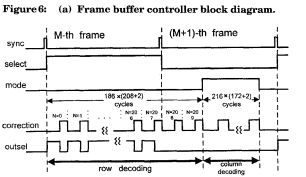

En la Figura 6 (a) se muestra el controlador de memoria intermedia como se compone de un plano de dirección y un plano de datos. El plano de la dirección consiste en un generador de direcciones de fila y un generador de direcciones de columna,

Para la corrección de errores, por ejemplo, el contenido de memoria intermedia de trama, se lee el XOR con la fila o columna de valor de error y luego se escribe de nuevo en el mismo tiempo.

Como se muestra en la Figura 6 (b), los dos controladores del frame cambian sus funciones por el número de señales de control generada internamente o externamente

Referencias:

- "A Reed-Solomon Product-Code (RS-PC) decoder for DVD applications" http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=672548

La referencia aún no está bien formateada :P 3 pts extra teoría de info.

ResponderEliminar